Page 131 - ELT_15th July 2020_Vol 373_Part 2

P. 131

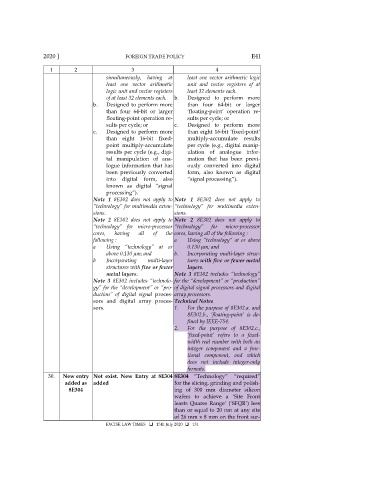

2020 ] FOREIGN TRADE POLICY E41

1 2 3 4

simultaneously, having at least one vector arithmetic logic

least one vector arithmetic unit and vector registers of at

logic unit and vector registers least 32 elements each.

of at least 32 elements each. b. Designed to perform more

b. Designed to perform more than four 64-bit or larger

than four 64-bit or larger ‘floating-point’ operation re-

floating-point operation re- sults per cycle; or

sults per cycle; or c. Designed to perform more

c. Designed to perform more than eight 16-bit ‘fixed-point’

than eight 16-bit fixed- multiply-accumulate results

point multiply-accumulate per cycle (e.g., digital manip-

results per cycle (e.g., digi- ulation of analogue infor-

tal manipulation of ana- mation that has been previ-

logue information that has ously converted into digital

been previously converted form, also known as digital

into digital form, also “signal processing”).

known as digital “signal

processing”).

Note 1 8E302 does not apply to Note 1 8E302 does not apply to

“technology” for multimedia exten- “technology” for multimedia exten-

sions. sions.

Note 2 8E302 does not apply to Note 2 8E302 does not apply to

“technology” for micro-processor “technology” for micro-processor

cores, having all of the cores, having all of the following :

following : a Using “technology” at or above

a Using “technology” at or 0.130 µm; and

above 0.130 µm; and b. Incorporating multi-layer struc-

b Incorporating multi-layer tures with five or fewer metal

structures with five or fewer layers.

metal layers. Note 3 8E302 includes “technology”

Note 3 8E302 includes “technolo- for the “development” or “production”

gy” for the “development” or “pro- of digital signal processors and digital

duction” of digital signal proces- array processors.

sors and digital array proces- Technical Notes

sors. 1. For the purpose of 8E302.a. and

8E302.b., ‘floating-point’ is de-

fined by IEEE-754.

2. For the purpose of 8E302.c.,

‘fixed-point’ refers to a fixed-

width real number with both an

integer component and a frac-

tional component, and which

does not include integer-only

formats.

30. New entry Not exist. New Entry at 8E304 8E304 “Technology” “required”

added as added for the slicing, grinding and polish-

8E304 ing of 300 mm diameter silicon

wafers to achieve a ‘Site Front

leasts Quares Range’ (‘SFQR’) less

than or equal to 20 nm at any site

of 26 mm x 8 mm on the front sur-

EXCISE LAW TIMES 15th July 2020 131